# Ahead of Time Generation for GPSA Protection in RISC-V Embedded Cores

# Abstract

State-of-the-art hardware countermeasures against fault attacks are based, among others, on control flow and code integrity checking. These integrities can be asserted by Generalized Path Signature Analysis and Continuous Signature Monitoring. However, supporting such mechanisms requires a dedicated compiler flow and does not support indirect jumps. In this work we propose a technique based on a hardware/software runtime to generate those signatures while executing unmodified COTS RISC-V binaries. The proposed approach has been implemented on a pipelined rv32i processor, and experimental results show an average slowdown of  $\times 1.82$  compared to unprotected implementations while being completely compiler independent.

# Introduction

Because of their nature, embedded systems are prone to physical attacks. Several works have demonstrated that a well-designed cryptographic application, whose implementation is considered safe, can be compromised with fault injection attacks (eg., laser, EM, clock or power glitch), which induce an incorrect behavior of the victim processor or a data leak [1].

Countermeasures against such faults can be implemented both in software or in hardware. Software countermeasures, often inserted at compile time, consist of duplicating part of the instructions to detect and counter fault injections. This type of countermeasures has reached its limits with the emergence of attacker models allowing for several faults happening in a single execution. On the other hand, hardware countermeasures rely on a modified processor microarchitecture which ensures some form of Control Flow Integrity (CFI) and code integrity. Among the numerous existing techniques, Generalized Path Signature Analysis (GPSA) and Continuous Signature Monitoring (CSM) [2] happen to provide the best trade-off between sensitivity and area/performance overhead.

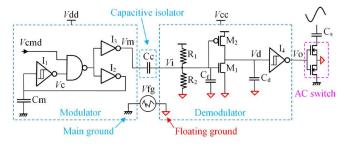

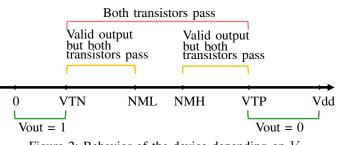

GPSA/CSM relies on cryptographic signatures to ensure integrity. Throughout the execution, the processor computes a signature based on previously executed instructions. The dynamic signature is verified against a reference signature at each branch and patches are used to correct the signature when executing branches. Additional instructions are therefore needed to load signatures during the execution. Besides, patches and reference signatures must be computed ahead of time and inserted in the executable.

In GPSA/CSM, the processor datapath is considered as being protected against faults, for example through error-detecting codes in both pipeline stage registers and data/code memory.

This technique is implemented in The SCI-FI RISC-V core [3], along with an additional mechanism that protects pipeline control signals through some form of redundancy.

SCI-FI and other existing approaches share common limitations: i) the target application needs a custom compilation flow to embed signature and patches; ii) indirect branches cannot be handled without strong assumptions on the possible targets; iii) function calls, returns, and interrupts require to store/restore signatures which increases attack surface.

Previous work [4] overcomes these limitations with a runtime environment for the generation of GPSA values. This solution comes with a high cost, in both time and area. Only relying on an interrupt mechanism and a routine to handle all the program GPSA values.

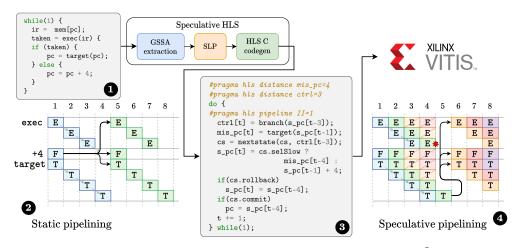

In this paper, we present a method to mitigate the high overheads induced by the method of Savary *et al.* [4]. Our approach relies not only on a runtime environment, but also on a GPSA value generation when deploying the program. Our runtime also transparently handles indirect branches, function calls, interrupts, and context switches.

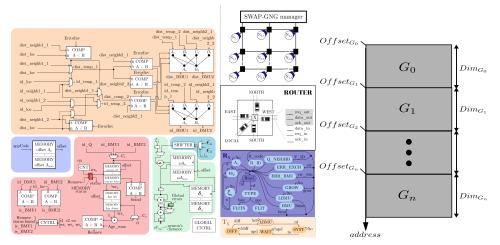

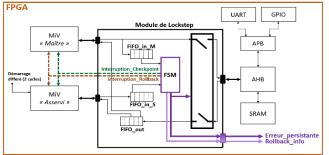

We have designed a proof of concept implementation based on the Comet RISC-V processor [5]. In our implementation, the pipeline is modified to check signatures on control flow instructions and trigger an interrupt to update patches and signatures whenever an indirect jump with missing signature is executed.

Our approach has been validated through fault injection simulations to ensure that protection was effective. The experimental study also shows that the average performance slowdown factor due to dynamic analysis is  $\times 1.82$ .

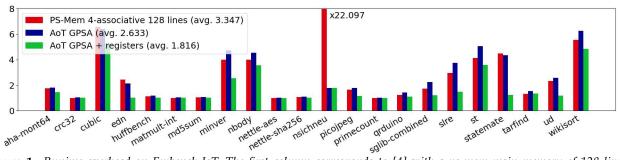

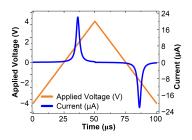

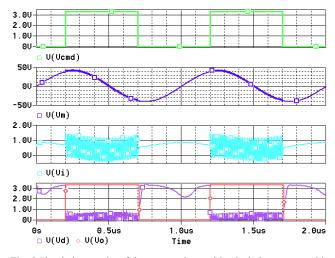

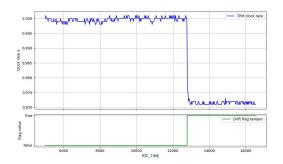

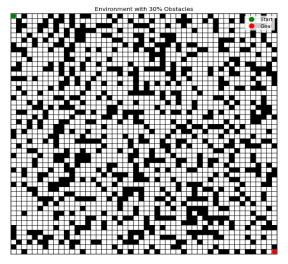

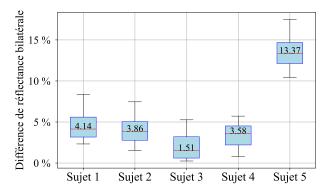

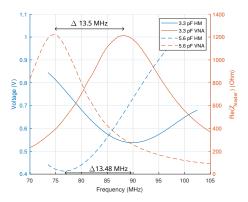

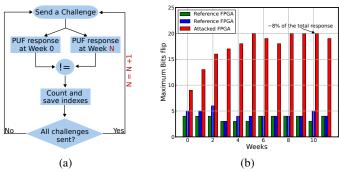

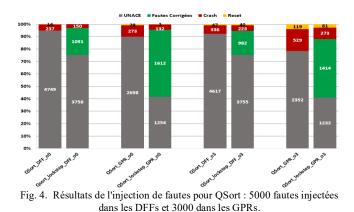

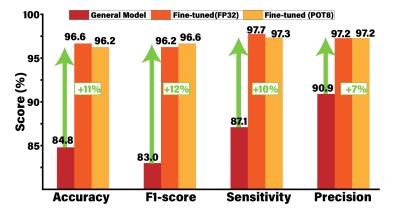

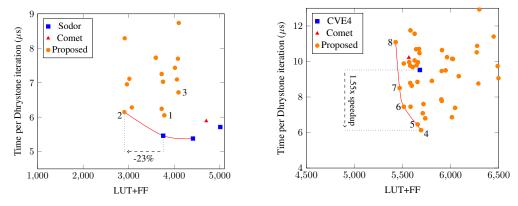

**Figure 1:** Runime overhead on Embench-IoT. The first column corresponds to [4] with a ps-mem main memory of 128 lines, 4-associative. **GPSA deploy** corresponds to the solution presented in this paper. **registers** correspond to two sets of 16 128bits register for indirect jumps, and other instructions, gpsa values.

# Ahead of Time Analysis for GPSA

In order to apply GPSA protection on COTS binaries, but with less overheads than existing approaches, we propose to compute the GPSA values ahead of time. These values are then stored in data memory.

During execution, we need the hardware to easily access the GPSA values of the executed instruction. To do this, these values are stored with the following structure: a list of tuple, each corresponding to a control flow instruction, sorted by PC. To ease the data cache fetching in memory, the tuples addresses are align to the data cache line size. A register is also added to the core, pointing to the values of the next control flow instruction to be executed.

To browse the list of tuple in constant time, it is sorted by PC and a fourth value is contained in the tuples: the address offset. In the tuple corresponding to an instruction *a*, the offset is the difference between the address of this tuple and the address of the tuple corresponding to the control flow instruction following the target of the instruction *a*. With this structure, when the CCFI component processes a control flow instruction, it loads the data cache line containing the values of this instruction. With these values, it verifies the dynamic signature. If the branch is taken, the signature is updated and the address of the tuple corresponding to the next instruction is obtained by adding the offset to the current tuple address. Otherwise, the corresponding tuple is the following tuple in the list, because it is sorted by PC.

Concerning patches for indirect jumps, as their targets cannot be known ahead of time, their computation is left to an interrupt mechanism, similar to the one from Savary *et al.* [4].

# **Experimental study**

We implemented our solution on the Comet RISC-V processor. The overall area overhead has been evaluated thanks to an HLS tool and is presented in the Table 1.

The figure 1 shows the slowdown between the previous solution from Savary *et al.* [4] and our solution

| Core                 | area( $\mu m^2$ ) | overhead |

|----------------------|-------------------|----------|

| PS-Mem [4]           | 150311            | 126.6%   |

| AoT GPSA             | 74856             | 12.9%    |

| AoT GPSA + registers | 86130             | 29.9%    |

**Table 1:** Area overhead of different solutions. PS-Mem refers to solution from [4] with a 4-associative 128 lines main memory. AoT GPSA is the solution presented in this paper. Registers represents two sets of 16 128bits registers for GPSA values.

on the Embench-IoT benchmarks [6], normalized on the performances of an unmodified Comet. Results show a slow-down factor between 1.0 and 5.23, with an average of  $\times$ 1.82.

# Conclusion

In this paper, we propose a method to apply GPSA and CSM protections on unmodified binaries, with an average runtime overhead of  $\times 1.82$  and area overhead of 30%. As far as we know, this is the best hardware/software implementation for GPSA without compiler dependence and allowing integrity properties to hold while handling indirect jumps, function calls, interrupts as well as context switches.

# References

- J. Laurent et al. "Fault Injection on Hidden Registers in a RISC-V Rocket Processor and Software Countermeasures". In: DATE'19.

- [2] M. Werner et al. "Protecting the Control Flow of Embedded Processors against Fault Attacks". In: *Smart Card Research and Advanced Applications*. Springer International, 2016.

- [3] T. Chamelot et al. "SCI-FI: Control Signal, Code, and Control Flow Integrity against Fault Injection Attacks". In: DATE'22. IEEE.

- [4] L. Savary et al. "Hardware/Software Runtime for GPSA Protection in RISC-V Embedded Cores". In: DATE'25.

- [5] S. Rokicki et al. "What You Simulate Is What You Synthesize: Designing a Processor Core from C++ Specifications". In: *ICCAD 2019*. IEEE.

- [6] David Patterson et al. Embench: Open Benchmarks for Embedded Platforms. https://github.com/embench/embench-iot.

# Accelerating LWE-Based Post-Quantum Cryptography with Approximate Computing

Diamante Simone Crescenzo<sup>1</sup>, Emanuele Valea<sup>1</sup>, Alberto Bosio<sup>2</sup> <sup>1</sup>Univ. Grenoble Alpes, CEA, List, F-38000 Grenoble, France <sup>2</sup>Institut des Nanotechnologies de Lyon, École Centrale de Lyon, Lyon, France

Abstract—Conventional cryptographic algorithms rely on hard mathematical problems to ensure an appropriate level of security. However, with the advent of quantum computing, classical cryptographic algorithms have become vulnerable. For this reason, Post-Quantum Cryptography (PQC) algorithms have emerged, as they are designed to resist quantum attacks. Most PQC algorithms rely on the Learning With Errors (LWE) problem, where generating pseudo-random controlled errors is crucial. A well-known solution is the use of hash functions followed by error samplers, implemented according to specific error distributions, whose implementation is challenging. This paper provides a proof of concept demonstrating how Approximate Computing (AxC) can be exploited in LWE-based cryptographic algorithms to alleviate this implementation bottleneck. The main idea is to use AxC circuits to perform certain operations of the algorithm, introducing the required error for free thanks to the approximation. Our key contribution is demonstrating how AxC techniques can be effectively applied to LWE-based algorithms, highlighting a novel approach to generating and introducing the error. This concept has proven effective in an approximate implementation of the FrodoKEM algorithm, showing up to 2.19% improvement in performance.

# I. INTRODUCTION

The Learning With Errors (LWE) problem involves recovering a secret vector from linear equations perturbed by small, structured errors, typically drawn from a discrete Gaussian or other bounded distributions. It can be represented by the notation  $b = \mathbf{A} \cdot s + e$ , where  $\mathbf{A}$  is the coefficient matrix, s is the secret vector, e is the error vector, and b is the constant vector (usually employed as the public key). Its security derives from worst-case lattice problems, such as the *Shortest Vector Problem* (SVP) [1], which remain hard to solve even for quantum algorithms. The difficulty of distinguishing perturbed linear equations from random noise is the basis of LWE-based cryptography.

Error generation poses challenges due to its complex sampling chains: a True Random Number Generator (TRNG) produces a seed, expanded via a cryptographically secure hash function (often from the NIST FIPS 202 [2] standard), then transformed into a Gaussian distribution using an adhoc sampler [3]. While dedicated hardware solutions are still emerging [4], *Approximate Computing* (AxC) offers an alternative by trading accuracy for efficiency, reducing area, power, and execution time [5].

This paper explores AxC as an optimization strategy for LWE-based cryptography, replacing explicit error-generation

with approximation in matrix-vector multiplication. The FrodoKEM algorithm [6] directly descends from the LWE problem, but with b, s, and e instantiated as matrices instead of vectors. For this reason, we use it as a case study. We introduce errors via AxC-based digital operators, specifically approximate adders from EvoApproxLib [7], characterizing their error distribution. A proof-of-concept implementation emulates these adders in software to ensure functional correctness, while performance results assume hardware equivalence to precise adders.

Our key contribution is demonstrating that AxC effectively introduces errors in LWE-based cryptography, achieving a 2.04% reduction in FrodoKEM's key exchange execution time.

# II. IMPLEMENTING FRODOKEM WITH AXADDERS

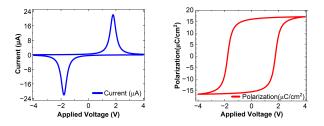

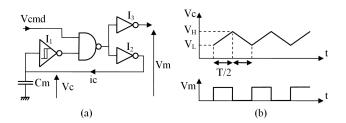

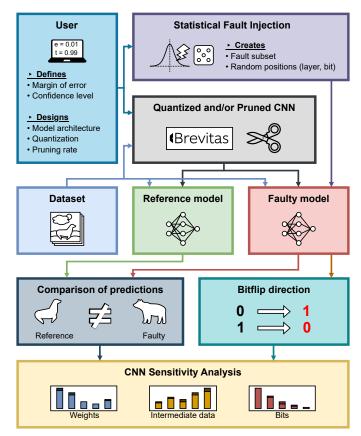

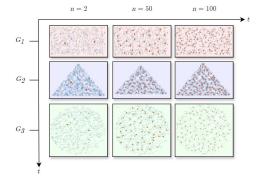

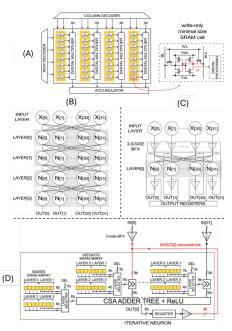

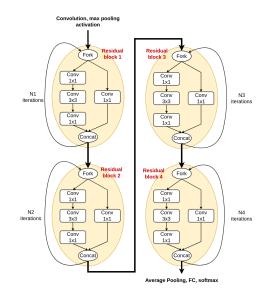

Our approximate FrodoKEM-640 software implementation is directly derived from the reference one<sup>1</sup>. We acted on the sections of code involving the error generation and addition in the *key generation* and *encryption* functions. A graphical highlevel overview of transitioning to an approximate version of the algorithm is available in Figure 1 for clarity. The diagram represents the standard algorithm implementation, with the greyed-out components highlighting the error generation chain that is removed due to the use of AxADD.

More specifically, all the function calls to the SHAKE128 primitive to generate the matrix  $\mathbf{e}$  were removed, which has a direct impact on performance. To introduce the necessary error in the scheme, we acted on the inner product  $\mathbf{A} \cdot \mathbf{s}$ . Equation 1 shows the computation details for each element  $b_{ij}$  of the public matrix  $\mathbf{b}$ . Each partial product is normally cumulated, with the exception of the last one, which is added to the partial result using the addu16\_0GN adder from [7].

$$b_{ij} = \sum_{k=0}^{n} a_{ik} s_{kj} = a_{i0} s_{0j} + \dots + a_{in} s_{nj}$$

(1)

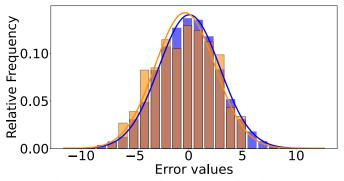

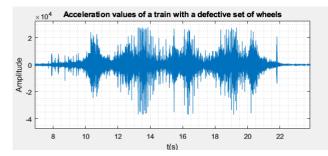

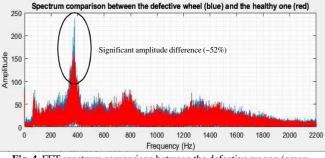

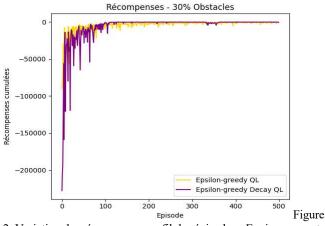

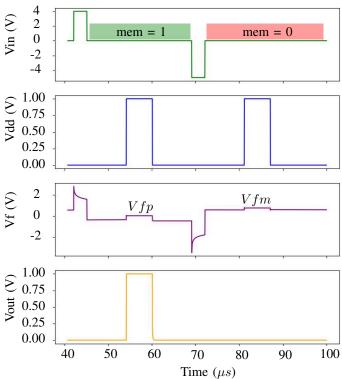

Its operation has been emulated by means of a C function call provided by the authors of [7]. Figure 2 compares the error distributions: the original FrodoKEM-640 errors (in blue) versus those from addu16\_0GN (in orange), along with their respective Gaussian fits. This adder was selected as the most suitable from the EvoApproxLib library based on its error characteristics.

This work was supported by CARNOT LIST AxPQC funding.

<sup>&</sup>lt;sup>1</sup>Available at: https://github.com/microsoft/PQCrypto-LWEKE

Fig. 1: Removing the error generation chain.

Fig. 2: Direct comparison of FrodoKEM-640 (in purple) and addu16\_0GN (in orange) error distributions.

Consequently, the errors no longer require the Gaussian sampling process, resulting in further performance improvements. The rest of the algorithm follows the reference implementation but with less pseudo-random data and optimized data structures. This approximate version of FrodoKEM-640 has been finally tested against the NIST KATs to check its proper functionality and performance.

## III. RESULTS

This study was performed on the reference FrodoKEM-640 C implementation<sup>1</sup> enriched with the modifications described in section II. The study was conducted on a Linux system with kernel version 4.18.0, an Intel Core i3-2120 CPU @ 3.30GHz, 16GB of RAM, and GCC version 8.5.0. The reported metrics are averages from multiple test vector runs, measured using the CPU Time Stamp Counter register.

Table I presents execution times (in clock cycles) for key generation, encryption, decryption, and a complete FrodoKEM run. The approximate implementation total cycles assume that an AxADD is implemented on board, replacing its execution time with that of a single operation. Parentheses indicate the percentage gain of AxADD over the reference FrodoKEM-640. The reduction in clock cycles exceeds that in generated bytes due to error generation overhead. Unlike simple random sampling, pseudo-random byte extraction from SHAKE128 requires additional function calls for setup and data retrieval,

TABLE I: AxFrodoKEM-640. Execution time in kilo clock cycles (kcc) and required number of bytes for error generation (B) for both reference implementation and with AxADD.

|                                   | KeyGen   | Encrypt  | Decrypt  | FrodoKEM  |

|-----------------------------------|----------|----------|----------|-----------|

| Execution Time<br>Reference (kcc) | 55,756   | 72,418   | 73,215   | 201,388   |

| Execution Time                    | 54,580   | 71,078   | 71,078   | 197,272   |

| AxADD (kcc)                       | (-2.11%) | (-1.85%) | (-2.19%) | (-2.04%)  |

| Error Generation<br>Reference (B) | 839,680  | 839,808  | 850,048  | 2,529,536 |

| Error Generation                  | 829,440  | 829,440  | 839,680  | 2,498,560 |

| AxADD (B)                         | (-1.22%) | (-1.23%) | (-1.22%) | (-1.22%)  |

followed by Gaussian sampling. As a result, FrodoKEM-640 achieves a 1.22% reduction in generated bytes, translating into a 2.04% decrease in execution time.

# **IV. CONCLUSION AND FURTHER PERSPECTIVES**

This paper demonstrates the feasibility of using Approximate Computing (AxC) to optimize Post-Quantum Cryptography (PQC), with FrodoKEM as a proof of concept. By employing approximate adders (AxADDs) to introduce errors, we achieved a 2.19% execution time improvement and a 1.23% reduction in generated bytes. While gains in FrodoKEM are limited by the large public matrix **A**, this study establishes AxC as a viable method for integrating error generation into LWE-based computations, suggesting broader applicability to other schemes with different structural properties.

Beyond performance, AxC raises considerations regarding entropy reduction due to the absence of explicit random error sampling. This analysis is beyond the scope of this paper. Future work could address this by randomizing the AxADD point in the approximate matrix inner product.

In summary, AxC offers a promising approach for improving LWE-based cryptographic schemes, opening avenues for further research in this promising area.

- [1] O. Regev, "On lattices, learning with errors, random linear codes, and cryptography," *J. ACM*, vol. 56, Sept. 2009.

- [2] "SHA-3 standard : Permutation-based hash and extendable-output functions," tech. rep., National Institute of Standards and Technology (US), 2015.

- [3] J. Howe, A. Khalid, C. Rafferty, F. Regazzoni, and M. O'Neill, "On practical discrete gaussian samplers for lattice-based cryptography," *IEEE Transactions on Computers*, vol. 67, no. 3, pp. 322–334, 2018.

- [4] D. S. Crescenzo, R. C. Rodriguez, R. Alidori, F. Bruguier, E. Valea, P. Benoit, and A. Bosio, "Hardware Accelerator for FIPS 202 Hash Functions in Post-Quantum Ready SoCs," in 2024 IEEE 30th International Symposium on On-Line Testing and Robust System Design (IOLTS), 2024.

- [5] J. Han and M. Orshansky, "Approximate computing: An emerging paradigm for energy-efficient design," in 2013 18th IEEE European Test Symposium (ETS).

- [6] E. Alkim, J. W. Bos, L. Ducas, P. Longa, I. Mironov, M. Naehrig, V. Nikolaenko, C. Peikert, A. Raghunathan, and D. Stebila, "FrodoKEM: Learning with errors key encapsulation." Submission to the NIST PQC Standardization Project, 2021. Available at: https://frodokem.org/files/ FrodoKEMspecification-20210604.pdf.

- [7] V. Mrazek, R. Hrbacek, Z. Vasicek, and L. Sekanina, "Evoapprox8b: Library of approximate adders and multipliers for circuit design and benchmarking of approximation methods," in *Design, Automation & Test* in Europe Conference & Exhibition (DATE), 2017, pp. 258–261, 2017.

# Low-Latency (i)FFT RTL Implementation for the FALCON Post-Quantum Signature Algorithm

Alexandre Ortega, Lilian Bossuet and Brice Colombier

Université Jean Monnet Saint-Etienne, CNRS, Institut d'Optique Graduate School, Laboratoire Hubert Curien UMR 5516,

F-42023, SAINT-ETIENNE, France

{alexandre.ortega; lilian.bossuet; b.colombier}@univ-st-etienne.fr

# I. INTRODUCTION

FALCON [1] is one of the three post-quantum digital signature schemes that have been recently standardized by NIST due to the future threat that quantum computers pose to classical cryptographic schemes [2]. Despite this, there is currently no full hardware register-transfer level (RTL) implementation of FALCON. One possible explanation is the rather unusual requirement for a double-precision floating-point Fast Fourier Transform (FFT) [3], which is used in FALCON to speed up polynomial multiplication. In this work, we propose a full RTL constant-time implementation of the FFT and its inverse (iFFT), on FPGA, tailored for the specific context of FALCON. Section II presents the FFT in the context of FAL-CON before Section III describes the proposed architecture. Afterwards, the performances of the proposed implementation are detailed and compared with previous works in Section IV. Section V concludes.

# II. THE FAST FOURIER TRANSFORM IN FALCON

In FALCON, the FFT over the ring  $\mathbb{Q}[x]/(\phi)$  is used with  $\phi = x^N + 1$  and  $N = 2^k$  a power of two. N is a security parameter of FALCON that can be equal to either 512 or 1024. Due to FALCON security requirements, IEEE-754 compliant double-precision floating-point arithmetic is being used [1]. Using the fact that FALCON polynomials are in  $\mathbb{Z}[x]/(\phi)$ , as well as the roots of unity symmetry in  $\mathbb{Z}[x]/(\phi)$ , the storage requirements can be halved and more than half of the computations can be omitted [1]. Before the optimizations, the amount of computations to perform is:

$$\#Ops = \log_2(N) \times \frac{N}{2} \tag{1}$$

After applying the optimizations, (1) becomes:

$$#Ops = (\log_2(N) - 1) \times \frac{N}{4}$$

(2)

# III. DESCRIPTION OF THE PROPOSED HARDWARE ARCHITECTURE

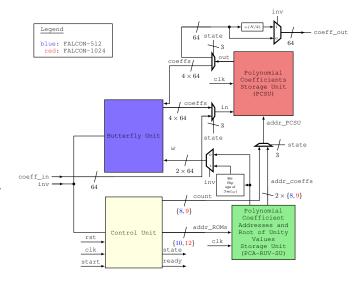

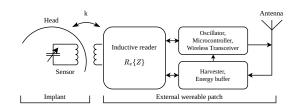

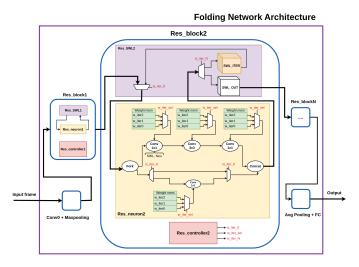

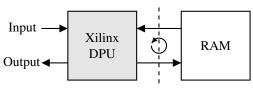

Fig. 1 shows the proposed hardware architecture. On top of a reset and clock signals, the input signals are:

- start is used to make the component start the computation of either the FFT or the iFFT.

- inv is used to choose between performing the FFT or the iFFT.

Fig. 1. Block diagram of the proposed hardware architecture of the (i)FFT for FALCON

• coeff\_in is a 64-bit bus used to stream in the coefficients of the input polynomial to transform.

The outputs are:

- ready indicates that the component has finished performing the computations and is streaming out the result.

- coeff\_out is a 64-bit bus used to stream out the coefficients of the result.

The proposed design is divided in four main blocks.

1) The butterfly unit: Made with three complex doubleprecision floating-point operators, an adder as well as a subtractor and a multiplier, it can be reconfigured dynamically to perform either the radix-2 decimation-in-time FFT or the radix-2 decimation-in-frequency iFFT.

2) The Polynomial coefficients storage unit: Two true dual port RAMs are used to store the polynomial coefficients. One RAM stores the real parts of the polynomial coefficients and the other RAM stores their imaginary parts. For FALCON-512, polynomials have 512 coefficients. Only the real and imaginary parts for the first half of these coefficients are stored as explained in Section II, so the two RAMs will each store 256 double-precision floating-point values with 8bit addresses. A double-precision floating-point value is stored on 64 bits (i.e. 8 bytes). Hence, the RAMs will each store  $256 \times 8 = 2.048$  kB. An identical reasoning with FALCON-1024 gives a 9-bit address bus and two RAMs each storing  $512 \times 8 = 4.096$  kB.

3) The Polynomial Coefficient Addresses and Root of Unity Values Storage Unit: Four single-port ROMs and one dualport ROM are used to store the pre-computed coefficient addresses in RAM and root of unity values. For each butterfly operation, two complex coefficients and one complex root of unity are used. Two single-port ROMs are used to store the pre-computed coefficient addresses in RAM. Using (2), it is determined that 1024 butterfly operations are required for the 512-coefficient (i)FFT, and 2304 for the 1024-coefficient (i)FFT. As the RAMs each store 256 values for the 512coefficient (i)FFT and 512 values for the 1024-coefficient (i)FFT, an 8-bit wide adress bus, for the two ROMs, is required for the 512-coefficient (i)FFT and an 9-bit wide address bus is required for the 1024-coefficient (i)FFT. This gives a storage requirement of  $1024 \times (8/8) = 1024 \times 1 = 1.024 \text{ kB}$  and  $2304 \times (9/8) = 2.592 \,\mathrm{kB}$  respectively for the 512-coefficient and the 1024-coefficient (i)FFT.

The choice was made to only store once the 64-bit values that can be used for either the real part or the imaginary part in one dual-port ROM and to store the sequence in which those values are used in two single-port ROMs. The reason for that choice was to reduce the amount of memory required to store the values needed for the root of unity. If the root of unity values to be used are stored consecutively in a straightforward manner, which means that repetitions are possible in the dual-port ROM,  $1024 \times 8 = 8.192 \,\mathrm{kB}$  are needed for the 512-coefficient (i)FFT and  $2304 \times 8 = 18.432 \,\text{kB}$  for the 1024-coefficient (i)FFT. If the root of unity values are stored only once along with the order in which they are accessed, 382 values need to be stored in the dual-port ROM which corresponds to  $382 \times (64/8) = 3.056 \text{ kB}$ , and 1024 addresses coded on 9 bits in both single-port ROMs which corresponds to  $2 \times 1024 \times (9/8) = 2 \times 1152 = 2.304$  kB. This means that this solution requires 3056 + 2304 = 5.36 kB of storage capacity for the 512-coefficient (i)FFT, which is a reduction of 34.6% compared with the straightforward solution. An identical reasoning, gives a storage requirement of 11.888 kB for the 1024-coefficient (i)FFT, which represents a reduction of 35.5% compared with the straightforward solution. Hence, instead of only one dual-port ROM, two single-port and one dual-port ROMs are used to store the root of unity values.

Concerning the root of unity values for the iFFT, their real parts are the same as the root of unity for the FFT and their imaginary parts are of opposite sign. Hence, only the values for the FFT are stored. When performing the iFFT the same values are read from the ROM, but not in the same order. Indeed, to perform the FFT operations, the addresses are read consecutively starting from the highest value. To perform the iFFT operations it is the opposite, the addresses are read consecutively starting from zero. Additionally, the sign bit of the imaginary part of the root of unity value is flipped.

*4) The Control Unit:* The control unit purpose is to manage the dataflow of the (i)FFT.

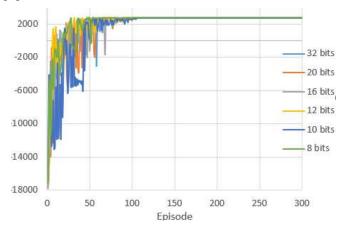

TABLE I

(I)FFT-512/(I)FFT-1024 IMPLEMENTATION RESULTS

|                          | This work |      | [4]    | Vivado 2023.2 |      |

|--------------------------|-----------|------|--------|---------------|------|

| Floating-point precision | Double    |      | Double | Single        |      |

| FFT length               | 512       | 1024 | 512    | 512           | 1024 |

| LUT                      | 9658      | 9677 | 8396   | 1741          | 1793 |

| FF                       | 369       | 374  | 2526   | 3468          | 3508 |

| DSP                      | 36        | 36   | 9      | 10            | 10   |

| BRAM                     | 8         | 11   | 9.5    | 4             | 5    |

| Latency (cycles)         | 3074      | 6658 | 19800  | 4589          | 9474 |

#### IV. RESULTS AND COMPARISONS WITH PREVIOUS WORKS

The proposed hardware implementation is described in VHDL and synthetised using AMD-Xilinx Vivado 2023.2. Table I reports the implementation results of the proposed design and compares it with the Vivado 2023.2 (i)FFT IP, and a co-design implementation of FALCON (i)FFT for the security parameter N = 512 [4]. The FPGA targetted, in all the reported results in Table I, is the AMD-Xilinx ZCU104+ (xczu7ev-ffvc1156-2-e) FPGA. The fairest comparison is with Mandal et al [4]. design as both design use double-precision. Both have similar metrics for the LUTs and the BRAMs. The proposed design uses  $4 \times$  more DSP blocks but around  $6.5 \times$ less FFs and clock cycles. As expected when comparing the proposed design to Vivado's IP, which uses single-precision, it uses around  $2 \times$  more BRAMs, more LUTs and DSPs. However, the proposed design uses around  $10 \times$  less FFs and achieves a lower latency.

## V. CONCLUSION

A low-latency full hardware constant-time RTL implementation of the (i)FFT, tailored for FALCON parameters, was presented. It achieves the best latency of the literature among FPGA-based implementations. This work addresses one of the major difficulties reported concerning the full hardware implementation of FALCON. This work can be used as an essential building block for future hardware implementation works on FALCON.

## ACKNOWLEDGMENT

This work received funding from the France 2030 program, managed by the French National Research Agency under grant agreement No. ANR-22-PETQ-0008 PQ-TLS.

- [1] P.-A. Fouque, J. Hoffstein, P. Kirchner, V. Lyubashevsky, T. Pornin, T. Prest, T. Ricosset, G. Seiler, W. Whyte, Z. Zhang, et al., "Falcon: Fast-Fourier lattice-based compact signatures over NTRU," *Submission to* the NIST's post-quantum cryptography standardization process, vol. 36, no. 5, pp. 1–75, 2018.

- [2] NIST, "Nist Announces First Four Quantum-Resistant Cryptographic Algorithms," https://nist.gov/news-events/news/2022/07/nist-announcesfirst-four-quantum-resistant-cryptographic-algorithms, 2022.

- [3] L. Beckwith, D. T. Nguyen, and K. Gaj, "High-Performance Hardware Implementation of Lattice-Based Digital Signatures." Cryptology ePrint Archive, Paper 2022/217, 2022.

- [4] S. Mandal and D. Roy, "Design of a Lightweight Fast Fourier Transformation for FALCON using Hardware-Software Co-Design," in *GLSVLSI'24 Proceedings*, pp. 228–232, 06 2024.

# Approximate Computing for Cryptography: Leveraging FD-SOI Back-Gate Scaling in LPPN

Andrea Marenco<sup>1</sup>, Emanuele Valea<sup>1</sup>, Elena Ioana Vatajelu<sup>2</sup> <sup>1</sup>Univ. Grenoble Alpes, CEA, List, F-38000 Grenoble, France <sup>2</sup>Univ. Grenoble Alpes, CNRS, Grenoble INP, TIMA, 38000 Grenoble, France

Abstract—The increasing use of digital communications has intensified the need for secure and cost-effective cryptographic implementations, especially in the Internet-of-Things (IoT). Post-Quantum Cryptography (PQC) schemes like Learning with Errors (LWE) and Learning Parity with Noise (LPN) rely on error distributions that are complex to generate in hardware. The Learning Parity with Physical Noise (LPPN) approach replaces explicit error sampling with controllable computational inaccuracies. This work implements LPPN on 22nm Fully Depleted Silicon-On-Insulator (FD-SOI) technology, leveraging back-gate voltage scaling to generate errors. Experimental results show that this technique significantly improves error controllability, demonstrating FD-SOI's potential for secure PQC applications.

# I. INTRODUCTION

The increasing reliance on digital communications has heightened concerns about security and privacy, especially in cost-sensitive IoT applications. Ensuring efficient and secure implementations of encryption primitives remains an engineering challenge. Hard learning problems, such as Learning with Errors (LWE) and Learning Parity with Noise (LPN), are the foundation of Post-Quantum Cryptography (PQC) [1]. These schemes rely on matrix-vector operations perturbed by noise from specific distributions, making error generation a crucial aspect. Traditional approaches require complex twophase sampling chains, which are hard to implement securely in hardware [2].

To address this, the Learning Parity with Physical Noise (LPPN) scheme replaces external error sampling with internal computational inaccuracies [3]. First demonstrated via Over-Scaling on 65nm technology, its feasibility on advanced nodes is unclear. In this work, we implement LPPN on 22nm FD-SOI technology, exploring back-gate voltage scaling as a more precise method for error control. Experimental results from on-chip measurements demonstrate its effectiveness, highlighting FD-SOI's potential for secure PQC implementations.

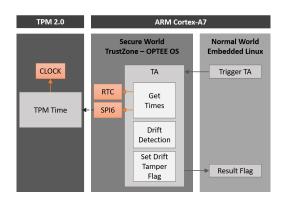

## **II. EXISTING IMPLEMENTATIONS OF LPPN**

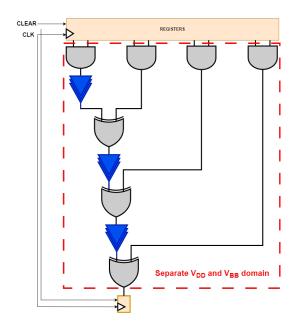

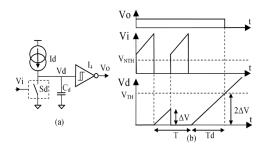

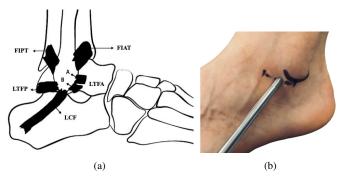

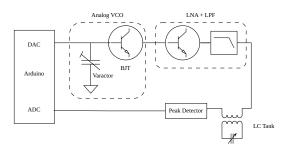

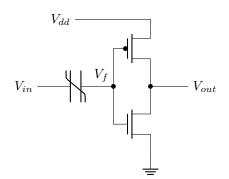

The core of the LPN problem is a dot product  $\langle x, k \rangle$  of two N-bit binary vectors, which can be computed using bitwise AND followed by N-1 XOR gates. Figure 1 shows an example of a serial hardware architecture for N = 4. Kamel et al. [3] introduced LPPN applying Over-Scaling to the dot product computation, inducing a controllable error by lowering the supply voltage. This occurs due to timing violations when the propagation delay causes the signal to be sampled by the output flip-flop before it has stabilized,

causing incorrect outputs with probability  $\epsilon$ . This probability is shown to be proportional to the supply voltage. However, the results from [3] are based on SPICE simulations on a 65nm node. In this paper, we demonstrate the same principle on a 22nm FD-SOI process, showing that the controllability of  $\epsilon$  is more complex. To address this, we propose back-gate voltage scaling as an alternative to Over-Scaling. By applying Reverse Body Biasing (RBB) to the critical path cells, we increase the threshold voltage  $V_T$  and slow down propagation, intentionally generating timing violations. This method provides a more precise control over  $\epsilon$ , offering a novel way to tune error probabilities in approximate circuits.

Fig. 1. Architecture for a 4-bit binary inner product, including delaying buffers at each stage of the XOR reduction chain.

# **III. FD-SOI-BASED LPPN IMPLEMENTATION**

The LPPN module was designed at gate-level using System Verilog and synthesized with Synopsys Design Compiler. Place & Route was performed with Cadence Innovus using GlobalFoundries 22nm FD-SOI (GF22FDX) technology. A 128-bit serial architecture was chosen for cryptographic applications. As shown in Figure 1, four buffers were added between stages to meet critical path constraints, closely tied to the circuit's clock frequency. The inner product module has a dedicated power domain, enabling independent supply voltage Over-Scaling and back-gate voltage scaling with respect to the rest of the circuit.

The LPPN module can operate in two modes:

- Fast Mode: performing multiple consecutive operations without resetting the input and output registers. In this mode, errors generated by the operation i depend on the results of the operation i 1.

- Slow Mode: it introduces a reset mechanism between consecutive operations, ensuring that each computation starts from a reset state. This reset allows to generate errors independently of the previous output value.

# **IV. ON-CHIP MEASUREMENTS**

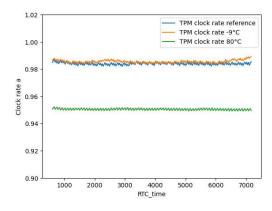

In order to compare the controllability of the error provided by Over-Scaling and back-gate voltage scaling, measurements were conducted on-silicon at room temperature ( $25^{\circ}$ C) for the Fast Mode and Slow Mode scenarios.

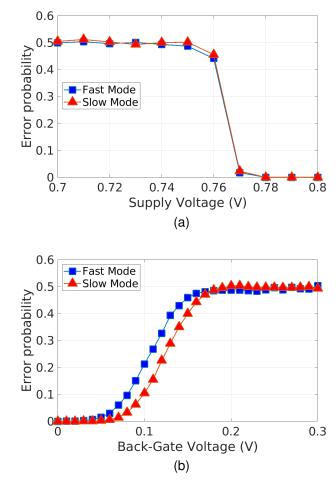

Fig. 2. On-chip measurement results. (a) Supply voltage sweep. (b) Back-gate voltage sweep.

The measurement protocol consisted in loading and clearing the needed operands depending on the scenario, executing the computation and comparing the result to the expected errorfree output. Ten thousands computations were carried out for each error point calculation. For each scenario two separate parameter sweeps were performed:

- On supply voltage V<sub>DD</sub> (Figure 2a) from 0.7 V to 0.8 V with 10 mV step.

- On back-gate voltage  $V_{BB}$  (Figure 2b) from 0 V to 0.3 V with 10 mV step.

Non-sweeping parameters were kept at their nominal values of 0.8 V for  $V_{DD}$  and 0 V for  $V_{BB}$ . The nominal clock frequency, which is the maximum frequency that generates no error, was determined to be 90 MHz. The results of these scenarios show an increase in  $\epsilon$  as  $V_{DD}$  decreases (or  $V_{BB}$ increases). To quantify this effect, we introduce the sensitivity of  $\epsilon$  with respect to  $V_{DD}$  (or  $V_{BB}$ ) denoted as  $S_{\epsilon}$ , and defined as:

$$S_{\epsilon} = \max\left(\frac{\Delta \epsilon}{|\Delta V|}\right)$$

A higher  $S_{\epsilon}$  value indicates greater difficulty in controlling the error probability with the chosen voltage scaling technique. Table I shows the sensitivity values from the sweeps. For both Fast and Slow scenarios, the sensitivity of the  $V_{BB}$  sweep is about four times smaller than that of the  $V_{DD}$  sweep, resulting in a much larger error tuning range.

TABLE I Error probability sensitivity  $(V^{-1})$

|                |           | SOTA                    | This work                    |

|----------------|-----------|-------------------------|------------------------------|

| Control method |           | Over-Scaling $(V_{DD})$ | Back-gate scaling $(V_{BB})$ |

| Sensitivity*   | Fast mode | 23.5                    | 5.9                          |

|                | Slow mode | 23.9                    | 6.5                          |

|                |           |                         |                              |

\* Lower is better

# V. CONCLUSIONS

This paper explores the implementation of the LPPN scheme on a 22nm FD-SOI process. Through on-chip measurements, we show that traditional Over-Scaling offers limited control over error probability at this technology node, raising concerns about its scalability. To address this, we propose and validate back-gate voltage scaling as a novel technique for better error control. Our results demonstrate that this approach improves error rate controllability, reducing sensitivity by up to four times compared to supply voltage scaling.

## ACKNOWLEDGMENT

This work was supported by the French National Research Agency (ANR) via the CARNOT LIST AxPQC funding.

- C. Peikert, "A decade of lattice cryptography." Cryptology ePrint Archive, Paper 2015/939, 2015.

- [2] D. Bellizia, N. E. Mrabet, A. P. Fournaris, S. Pontié, F. Regazzoni, F.-X. Standaert, É. Tasso, and E. Valea, "Post-quantum cryptography: Challenges and opportunities for robust and secure hw design," in 2021 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pp. 1–6, 2021.

- [3] D. Kamel, F.-X. Standaert, A. Duc, D. Flandre, and F. Berti, "Learning with physical noise or errors," *IEEE Transactions on Dependable and Secure Computing*, vol. 17, no. 5, pp. 957–971, 2020.

# Characterization and modelling of the thermal behavior of 55nm SiGe HBT

A. Sarafinof<sup>1</sup>, C. Mukherjee<sup>1</sup>, M. De Matos<sup>1</sup>, F. Cacho<sup>2</sup>, C. Maneux<sup>1</sup>

<sup>1</sup>IMS Lab, University of Bordeaux, Talence, France

<sup>2</sup>STMicroelectronics, Crolles, France

Abstract—In this paper, the thermal model of 55 nm SiGe HBT is investigated. Subsequently, we use the S-Parameters technique to extract the thermal impedance. DC and pulsed measurements are performed to obtain the parameters representative to the thermal behaviour. Afterwards, we present the comparison of our approach on measured data from two SiGe HBT technologies from STMicroelectronics, B55x and B55.

*Index Terms*—SiGe HBTs, thermal impedance, thermal network, self-heating, S-Parameters.

# I. INTRODUCTION

The miniaturization of the electronic devices and the increase of the power performance demand at high frequency due to the 5G and 6G requirements [1] lead to push HBT operation closer to their Safe Operating Area (SOA) limit [2]. This limit is defined by multiple limiting mechanisms such as the self-heating and the impact ionization defining the limit beyond which the device starts to degrade and become unstable. STMicroelectronics has enhanced its SiGe HBT technology [3], to face the 6G requirements, this new generation is called B55X [4]. The main upgrade of the device is related to his architecture allowing the heat to be dissipated more efficiently through the backend of line.

In this paper, the first part is dedicated to the thermal characterization to model the impact of this new device architecture on the thermal equivalent circuit. In a second phase, the device has been submitted to some pulsed measurements and compared to simulations .

# **II. THERMAL CHARACTERIZATION**

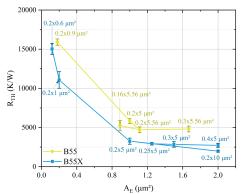

## A. Thermal Resistance

To extract the thermal resistance, the intersection method is used. By measuring Gummel plots for two different  $V_{CE}$ values and two different ambient temperatures TAMB, one collector current IC,int is extracted [5]. Then, using the equation (1), the thermal resistance is extracted. Among all the dimensions studied, ranging from emitter area  $A_E =$  $0.2x0.6\mu\text{m}^2$  to  $A_E = 0.4x5\mu\text{m}^2$ , the results shown in this paper are related to  $A_E = 0.2x5\mu\text{m}^2$ , which is considered as the main dimension.

$$R_{TH} = \frac{T_{amb,2} - T_{amb,1}}{I_{C,int}(V_{CE,1} - V_{CE,2})}$$

(1)

By observing the figure 1 comparing the thermal resistance of the two devices generations, the B55X shows a reduction of close to 40% compared to the B55. This RTH decrease is due to the B55X architecture optimized to reduce the self-heating thanks to the reduced thinness of the SSTI, lower than 100nm, allowing to expand the heat dissipation cone [6].

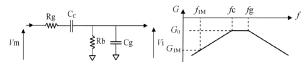

# B. Thermal impedance

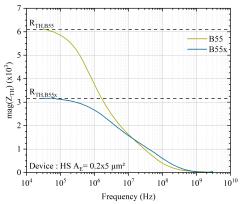

To extract the thermal impedance  $(Z_{TH})$ , the S-Parameters measurements are performed [7]. These measurements were achieved between 30kHz and 3GHz since the thermal behaviour appears dominant at low frequencies compared to the electrical one. To extract  $Z_{TH}$ , the equation (2) is used with  $Y_{ij}^{DC}$ , the value for the frequency close to 0 and  $Y_{ij}^{AC}$ , the Y-parameters corresponding to isothermal conditions.

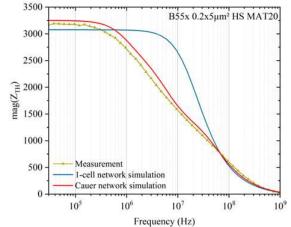

The figure 2 shows the plot of the magnitude of  $Z_{TH}$ . Two differences can be noted, the first one is related to the low frequency ( $_{1}105 \text{ Hz}$ ) value of each plot which represents the  $R_{TH}$  value. The second difference is the decrease behaviours as a function of the frequency. These different frequency behaviours are representative of the differences of heat dissipation through the device and therefore the architectural difference.

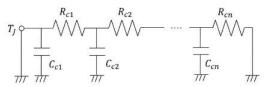

# C. Thermal network

The thermal network used in the current HiCuM simulation includes only one  $R_{TH}$ - $C_{TH}$  cell representing a single pole. A more accurate thermal pole representation is a network with three cells called Cauer Network as described on the figure 3. The Cauer network is an electrical representation of the different parts of the device architecture in terms of thermal representation.

The figure 4 permit to observe the extraction of this network. The objective is to match the plot from the equation of the network with the measurement plot. The magnitude of the simulated 3-cell thermal network is close to the measurement demonstrating a better representation than the previous 1-cell network proving the accuracy of the Cauer network. Another evidence of the accuracy of the 3-cell model compared to the single cell model is the pulsed measurement described in the next section.

# **III. PULSED MEASUREMENT AND SIMULATIONS**

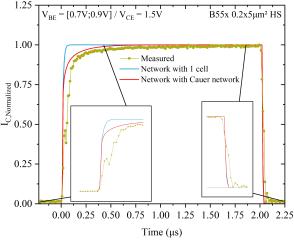

The difference between the two different network in simulation can be observe by performing transient simulations. To observe these differences, a pulsed voltage is sent to Base Emitter junction from 0.7V to 0.9V while keeping constant the Collector Emitter voltage at 1.5V [9]. Similarly, HiCuM simulations are performed with the 1-cell thermal network and with the modified thermal network with three cells.

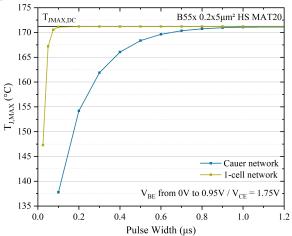

The results of the different simulations compared to measurements are presented in the figure 5. The normalize current reach 1 at  $I_C$  equal to his maximum value. The main difference with the modified network is the  $I_C$  values during the rise of the pulse. The network described by the three-pole thermal model shows better accuracy than 1-cell network confirming the S-Parameters analysis. The junction temperature  $(T_J)$  is also simulated to compare the two networks. The figure 6 represent the junction temperature maximum for different pulse widths. The temperature is really impacted by the pulse width because at low pulse width, the  $I_C$  does not reach his steady state and  $T_J$  does not reach the DC value.

# **IV. CONCLUSION**

For the first time, SiGe HBT B55X from STMicroelectronics has been characterized thermally. The thermal characterization shows a better heat dissipation compared to the precedent device generation resulting in a lower junction temperature thanks to a 40 % lower thermal resistance. The thermal behavior has been simulated with the extraction of the thermal network and the integration in the HiCuM model. Two network has been compared and the Cauer network is more accurate to the measurement than the 1-cell network. The next step is performing dynamic stress measurements to study their degradation mechanisms depending on the stress types.

- [1] E. C. Strinati et al., in 2022 EuCNC/6G Summit, june 2022, p. 423-428.

- doi: 10.1109/EuCNC/6GSummit549 41.2022.9815700. A. J. Scholten, in 2020 IEEE BCICTS, nov. 2020, p. 1-8. doi: 10.1109/BCICTS48439.2020.9392953. [2] Α.

- P. Chevalier et al, in 2014 IEEE International Electron Devices Meeting, [3] dec. 2014. doi: 10.1109/IEDM.2014 .7046978.

- P. Chevalier et al., in 2024 IEEE BCICTS, oct. 2024, p.13-17. doi: 10.1109/BCICTS59662.2024.10745707. [4]

- [5] M. Couret, "Failure mechanisms implementation into SiGe HBT compact model operating close to safe operating area edges", dec. 2020. C. Mukherjee et al., IEEE Trans. Electron Devices, vol.66, n°5, may

- [6] 2019. doi: 10.1109/TED.2019.2906979

- A. K. Sahoo et al., IEEE Electron Device Lett., vol.32, n°2, feb. 2011. doi: 10.1109/LED.2010.2091252. S. Fukunaga et T. Funaki, NOLTA, vol.11, n°2, 2020. doi: [7]

- [8]

- M. Couret et al., 2019 IEEE 32nd ICMTS, mar. 2019. doi: 10.1109/ICMTS.2019.8730964. [9]

Fig. 1: Thermal resistance with their error bars versus emitter area according to different emitter drawn dimensions of B55 and B55x

Fig. 2: Thermal impedance versus frequency for 0.2 x 5  $\mu m^2$  emitter area of B55 and B55x

Fig. 3: Electrical equivalent circuit of Cauer thermal network [8]

Fig. 4:  $Z_{TH}$  magnitude for different thermal networks

Fig. 5: Normalized collector current response as a function of time comparing measurement and simulations

Fig. 6: Simulation of  $T_{J,MAX}$  versus the pulse width for specific bias condition

# Vers une électronique embarquée pour l'instrumentation nucléaire et l'identification de particules

Julien Portanguen<sup>1,2</sup>, Gwenolé Corre<sup>1</sup>, Yoann Moline<sup>1</sup>, Jean-Michel Bourbotte<sup>1</sup>, Victor Buridon<sup>1</sup>, Wilfrid Husson<sup>1</sup>, Martial Owczaruk<sup>1</sup>, Vincent Métivier<sup>2</sup>

<sup>1</sup>Université Paris-Saclay, CEA, List, F-91120 Palaiseau, France

<sup>2</sup>SUBATECH, IMT Atlantique, Nantes Université, CNRS/IN2P3, F-44000 Nantes, France Contact : julien.portanguen@cea.fr

Résumé-Dans l'instrumentation nucléaire, le photodétecteur le plus répandu pour la scintillation est le tube photomultiplicateur (PMT). Une alternative est apparue il y a quelques années avec les photomultiplicateurs au silicium, ou SiPM. La discrimination des particules pour la non-prolifération nucléaire, la sécurité ou la sûreté reste un domaine dans lequel les SiPM sont moins efficaces que les PMT, malgré leur plus grande compacité et durabilité. Pour garantir les performances de discrimination de particules, il est essentiel de préserver les caractéristiques intrinsèques du signal. Les travaux menés ont cherché à obtenir un modèle complet du SiPM pour simuler leurs réponses à des interactions gammas et neutrons du scintillateur jusqu'à l'étage de numérisation. Un script Python a permis de générer des modèles SPICE de SiPM pour un nombre de détections et des caractéristiques variables. Des expériences de scintillation ont fourni des données d'entrée réalistes pour les temps d'arrivée des photons sur le photodétecteur. Enfin, des comparaisons d'architectures de préamplification ont montré un impact sur les capacités de discrimination du SiPM.

Index Terms—Modèle électrique équivalent, discrimination neutron-gamma, scintillateur, identification de particules, silicon photomultiplier (SiPM), simulation program with integrated circuit emphasis (SPICE)

# I. INTRODUCTION

L'instrumentation nucléaire répond à diverses applications telles que l'imagerie médicale et astronomique, la sûreté ou la sécurité. Les rayonnements ionisants déposent aléatoirement leur énergie dans les détecteurs au cours du temps sous forme d'impulsions. L'objectif est de mesurer les caractéristiques de ces impulsions qui varient en fonction de l'application. Notre cadre applicatif s'intéresse à la discrimination de particules à l'aide de systèmes portables pour la caractérisation des sources ou la radioprotection [1]. Nous réalisons des mesures avec un scintillateur plastique sur un photomultiplicateur silicium (SiPM) dans l'objectif de concevoir un système embarqué. Ces détecteurs génèrent une lumière dans le domaine visible à la suite d'une interaction avec un rayonnement ionisant. Les tubes photomultiplicateurs (PMT) et les SiPM sont les deux technologies utilisées pour la collecte des photons. Les SiPM autorisent des systèmes plus compacts et mécaniquement plus durables que ceux utilisant des PMT. Malgré un gain et un bruit sensibles à la température, les SiPM nécessitent une

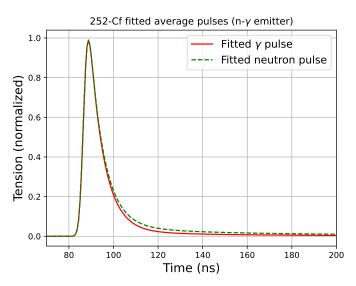

tension de fonctionnement plus faible que les PMT, typiquement 30 V contre 1000 V, et ne sont pas affectés par les champs magnétiques ni détruits par la lumière directe [2]. Un signal généré par l'ensemble scintillateur et SiPM aura généralement une décroissance de quelques centaines de nanosecondes et une amplitude de quelques millivolts. Dans notre cas, nous essayons de séparer les interactions  $\gamma$  des interactions neutroniques. La distinction entre ces impulsions réside dans la forme de l'impulsion et est l'une des plus difficiles parmi les différentes particules ionisantes car la différence est ténue. Des impulsions normalisées de scintillateur plastique sont présentées en figure 1. La discrimination des particules dans les systèmes embarqués est généralement réalisée par la méthode Pulse Shape Discrimination (PSD) [3]. Cette méthode repose sur le calcul de deux intégrales appelées par la suite  $Q_{\text{tail}}$  et  $Q_{\text{total}}$ . Ces intégrales sont calculées pour chaque impulsion en fixant l'instant de début des portes d'intégration et leur durée. Le ratio Tail-To-Total (TTT) prend en compte ces deux intégrations de la manière suivante :

$$\text{FTT-ratio} = \frac{Q_{\text{tail}}}{Q_{\text{total}}}.$$

(1)

Cette technique est facile à mettre en œuvre sur des architectures intégrées comme des FPGA. Ce papier propose de définir des modèles de simulation de SiPM qui permettent une comparaison avec les PMT en s'appuyant sur des données d'entrée réalistes afin d'en conserver le sens physique. La section II décrit le protocole expérimental et les résultats ayant permis l'obtention de ces données. La section III décrit la génération du modèle SPICE de SiPM. Enfin la section IV décrit succintement les travaux en cours sur l'électronique pour les SiPM dont certains résultats ont été soumis récemment.

## II. ACQUISITION DE DONNÉES D'ENTRÉE

Pour notre application, nous avons besoin de données de scintillation réalistes. Nous avons mené des expériences avec du Cs-137 (émission  $\gamma$ ) et du Cf-252 (émissions neutroniques et  $\gamma$ ). Pour obtenir ces impulsions, nous avons mis en place un banc d'essai composé d'un PMT H11284-MOD Hamamatsu et d'un scintillateur plastique EJ-276 d'Eljen Technology. Des

études internes ont montré que ce PMT était le meilleur candidat pour la discrimination  $n/\gamma$ . L'EJ-276 est l'un des scintillateurs plastiques classiquement utilisés dans la littérature et fournit un point de départ cohérent pour la discrimination. Les impulsions collectées sont traitées en Python a posteriori. Nous avons ajusté la triple décroissance exponentielle du scintillateur convolué par la fonction de transfert gaussienne du PMT. La chaîne de mesure combine ces deux contributions, qui forment une gaussienne modifiée exponentielle. Ces résultats sont comparés aux données du fabricant. Par concision, tous ces résultats seront présentés lors du colloque du GDR SOC<sup>2</sup>.

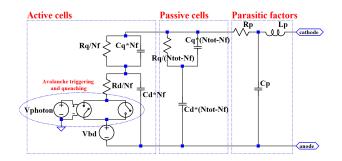

# III. MODÈLES POUR LA SIMULATION ÉLECTRIQUE

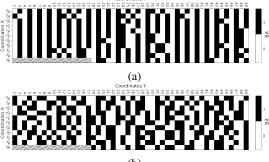

Les codes Monte Carlo tels que Geant4, MCNP ou PHITS sont adaptés à la simulation de la physique des scintillateurs. Ils fournissent une représentation de la probabilité d'interaction et de l'énergie déposée associée. Cependant, les modèles SiPM ont encore leurs limites pour la photodétection. Les premiers étaient axés sur le modèle équivalent électrique de la diode à avalanche pour photon unique (SPAD) [4]. La figure 2 montre un modèle SPICE couramment utilisé dans la littérature [5] et sur lequel le développement s'est basé. Ces modèles ont été appliqués exclusivement à des sorties de photons uniques (ou multiples simultanés) à des fins de validation du modèle. Des modèles plus complexes ont ensuite pris en compte un plus grand nombre de photons, survenant à différents moments [6], [7]. Ces modèles ont été conçus pour les besoins de la spectrométrie  $\gamma$ , et nous voulons maintenant aller plus loin avec des objectifs de discrimination de la forme de l'impulsion. Un script Python a été développé pour écrire la netlist automatiquement. Cette approche permet de modifier tous les paramètres pour configurer n'importe quel SiPM. Le nombre de cellules actives et totales, l'impédance de quenching, l'impédance équivalente ou l'impédance de lecture peuvent être modifiées. Le modèle SPICE créé peut activer

FIGURE 1. Impulsions moyennes  $\gamma$  et neutron en tension en sortie d'un ensemble scintillateur et PMT (ajustées)

FIGURE 2. Modèle électrique équivalent de SiPM [5] pour  $N_f$  cellules activées et  $N_{tot} - N_f$  cellules passives.  $R_Q$  et  $C_Q$  représentent l'impédance de *quenching*,  $R_D$  et  $C_D$  le modèle équivalent de diode,  $V_{photon}$  déclenche l'avalanche,  $V_{bd}$  est la tension d'avalanche,  $R_P$ ,  $C_P$  et  $L_P$  représentent les éléments parasites.

les SPAD à différents moments grâce à un fichier d'entrée. Comme le modèle ne peut pas gérer les phénomènes physiques stochastiques, ceux-ci sont inclus dans ce fichier d'entrée. Nous simulons également les effets secondaires induits par le SiPM, tels que les courants d'obscurité, la diaphonie ou les impulsions secondaires de cette façon. Cette approche permet de simuler n'importe quelle stimulation photonique en utilisant la spécification technique du SiPM. Par concision, ces résultats seront présentés lors du colloque.

# IV. CONCLUSION ET PERSPECTIVES

Les travaux présentés permettent de définir la capacité théorique atteignable de discrimination d'un SiPM. Ce travail préliminaire a été réalisé en vue de la conception d'une électronique spécifique (ASIC) pour la discrimination  $n/\gamma$ . Nous travaillons actuellement sur une étude comparative de préamplificateurs pour optimiser les performances de discrimination  $n/\gamma$  en utilisant des SiPM.

# RÉFÉRENCES

- J. Adams and G. White, "A versatile pulse shape discriminator for charged particle separation and its application to fast neutron time-offlight spectroscopy," *Nuclear Instruments and Methods*, vol. 156, no. 3, pp. 459–476, 1978.

- [2] E. Roncali and S. R. Cherry, "Application of silicon photomultipliers to positron emission tomography," *Annals of biomedical engineering*, vol. 39, pp. 1358–1377, 2011.

- [3] M. Grodzicka-Kobylka, T. Szczesniak, M. Moszyński, K. Brylew, L. Swiderski, J. Valiente-Dobón, P. Schotanus, K. Grodzicki, and H. Trzaskowska, "Fast neutron and gamma ray pulse shape discrimination in ej-276 and ej-276g plastic scintillators," *Journal of Instrumentation*, vol. 15, no. 03, p. P03030, 2020.

- [4] F. Corsi, A. Dragone, C. Marzocca, A. Del Guerra, P. Delizia, N. Dinu, C. Piemonte, M. Boscardin, and G. F. Dalla Betta, "Modelling a silicon photomultiplier (sipm) as a signal source for optimum front-end design," *Nuclear Instruments and Methods in Physics Research Section A : Accelerators, Spectrometers, Detectors and Associated Equipment*, vol. 572, no. 1, pp. 416–418, 2007.

- [5] F. Acerbi and S. Gundacker, "Understanding and simulating sipms," Nuclear Instruments and Methods in Physics Research Section A : Accelerators, Spectrometers, Detectors and Associated Equipment, vol. 926, pp. 16–35, 2019.

- [6] K. D. McGee, "Silicon photomultiplier modeling of csi (tl) with front end electronics using a monte carlo model," 2019.

- [7] A. K. Jha, H. T. Van Dam, M. A. Kupinski, and E. Clarkson, "Simulating silicon photomultiplier response to scintillation light," *IEEE transactions* on nuclear science, vol. 60, no. 1, pp. 336–351, 2013.

# Enhancing Keystone Security Against Cache Timing Attacks: A Modular Approach

Oussama Elmnaouri<sup>\*</sup>, Pascal Cotret<sup>\*</sup>, Vianney Lapôtre<sup>†</sup>, Loïc Lagadec<sup>\*</sup> \* Lab-STICC, UMR CNRS 6285, ENSTA (29806 Brest Cedex 9, France) firstname.lastname@ensta.fr <sup>†</sup> Lab-STICC, UMR CNRS 6285, Université de Bretagne-Sud (56100 Lorient, France) vianney.lapotre@univ-ubs.fr

Abstract—Confidential computing includes various methods to enhance data security, notably by processing sensitive information within Trusted Execution Environments (TEEs). However, TEEs remain vulnerable to Side-Channel Attacks (SCAs), such as cache timing attacks, which exploit timing variations to extract confidential data. Existing TEE designs do not provide sufficient protection against these threats, highlighting the need for stronger security measures. This study focuses on integrating countermeasures specifically targeting timing and cache vulnerabilities within a TEE. The implementation will leverage the RISC-V architecture to explore its potential in mitigating SCA

*Index Terms*—Computer Architecture, Confidential Computing, Hardware Security, TEEs, SCAs.

within TEE.

# I. INTRODUCTION

Trusted Execution Environments (TEEs) are essential for protecting sensitive data by providing isolated environments that guarantee both data confidentiality and integrity. Notable TEEs include proprietary solutions like ARM TrustZone [1], Intel SGX [2] and AMD SEV [3], as well as open source solutions such as Keystone [4] and Penglai [5] for RISC-V. While TEEs offer strong protection against numerous software attacks, they remain vulnerable to cache-based and timing side-channel attacks. These attacks exploit variations in execution time or cache access patterns to extract sensitive data, posing a major challenge to TEE security.

Microarchitectural cache timing attacks, such as Prime+Probe, Flush+Reload, and Evict+Time [6], pose significant challenges to the security of TEEs [7] as they can leak sensitive data by analyzing cache accesses. Various countermeasures have been proposed to mitigate these risks [6], but each comes with trade-offs, some cause high performance overhead, while others do not fully protect against all types of side-channel attacks.

# II. THREAT MODEL

The threat model considers that applications executing in both the Rich Execution Environment (REE) and the TEE are vulnerable to cache-based and transient execution sidechannel attacks [8]. The attacker is any application running on the system that shares the cache with the victim. This includes both untrusted applications in the REE and potentially malicious applications in the TEE. We do not consider physical attacks (e.g., fault injection, power analysis).

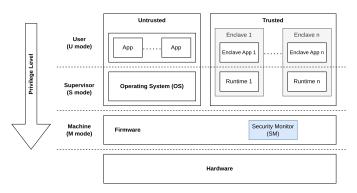

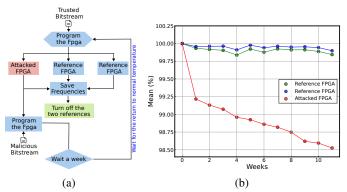

# **III. KEYSTONE STUDY**

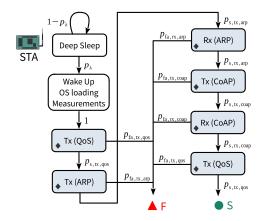

Keystone [4] is an open-source TEE designed for RISC-V processors, combining both security concepts from ARM TrustZone and Intel SGX to establish a clear separation between two execution domains. The non-secure world operates under normal processor conditions, running the untrusted operating system and normal applications while the secure world ensures the execution of sensitive applications, isolated from both the operating system and other applications (sensitive and normal). Keystone is based on a Security Monitor (SM) that manages the entire lifecycle of enclaves and ensures a secure communication between the two worlds by using the RISC-V Physical Memory Protection (PMP) [9] to enforce memory isolation, ensuring that confidential data and enclaves are safeguarded against unauthorized access, providing a flexible and efficient security framework. Figure 1 presents the architecture of a secure system based on enclaves, highlighting the different privilege levels and the separation between trusted and untrusted worlds.

Fig. 1. Keystone Architecture: Secure and Non-Secure World Isolation (adapted from [4]).

# IV. COUNTERMEASURES ON KEYSTONE

Various countermeasures have been developed to mitigate cache timing side-channel attacks [6], each addressing different vulnerabilities:

The work presented in this paper was realized in the frame of the SCAMA project number ANR-23-CE39-0011, supported by a grant of the French National Research Agency (ANR).

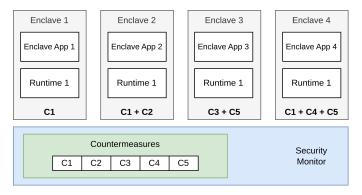

Fig. 2. Flexible Enclaves with Customizable Countermeasures library.

- **Constant-time execution:** Ensures that both cache access patterns and control flow remain independent of secret data, preventing any information leakage through cache timing attacks. This technique is widely used in cryptographic algorithms like AES to prevent key leakage due to execution time variations [10].

- Noise injection: Introduces randomness in timing measurements or accesses to shared resources to obscure variations exploitable by an attacker, thereby preventing the leakage of sensitive information. This technique is widely used in cryptographic implementations, real-time systems, and secure embedded devices [11], [12].

- Enforcing Determinism: Eliminates execution time variations that could be exploited by an attacker to extract sensitive information through timing channels. This technique is widely integrated in debugging frameworks, cloud computing, and virtual machines security [13], [14].

- Time Partitioning: Controls access to shared resources over time to prevent cache timing-based attacks. This is achieved through techniques that influence concurrent resource access and program transitions. This approach is widely used in countermeasures such as Cache Flushing [15], Lattice Scheduling [16], and Execution leases [17].

- Hardware Partitioning: Isolates hardware resources to prevent cache side-channel attacks by ensuring that each process has its dedicated space. This technique is widely used in countermeasures such as cache locking [18], Cache Coloring [19], and Quasi-Partitioning [20].

This work aims to develop a flexible and modular framework within Keystone. Although existing research primarily addresses individual mitigation techniques, our approach integrates these countermeasures into a unified framework, thereby providing users with enhanced flexibility to selectively enable the protections that best align with their specific security and performance requirements. One possible direction is to integrate these protections within the SM to enhance enclave lifecycle management and security [21]. However, this remains an open question, and further analysis is required to assess the feasibility, trade-offs, and effectiveness of such an approach. Figure 2 illustrates how we envision the Keystone structure with the integration of these security techniques and protections.

- B. Ngabonziza, D. Martin, A. Bailey, H. Cho, and S. Martin, "Trustzone explained: Architectural features and use cases," in *CIC*, pp. 445–451, 2016.

- [2] V. Costan and S. Devadas, "Intel SGX explained." Cryptology ePrint Archive, Paper 2016/086, 2016.

- [3] I. Advanced Micro Devices, "Amd sev-snp: Strengthening vm isolation with integrity protection and more," tech. rep., Advanced Micro Devices, Inc., January 2020. White Paper.

- [4] D. Lee, D. Kohlbrenner, S. Shinde, K. Asanović, and D. Song, "Keystone: an open framework for architecting trusted execution environments," in *EuroSys*, EuroSys '20, (New York, NY, USA), Association for Computing Machinery, 2020.

- [5] E. Feng, X. Lu, D. Du, B. Yang, X. Jiang, Y. Xia, B. Zang, and H. Chen, "Scalable memory protection in the PENGLAI enclave," in USENIX OSDI, pp. 275–294, USENIX Association, July 2021.

- OSDI, pp. 275–294, USENIX Association, July 2021.

[6] Q. Ge, Y. Yarom, D. Cock, and G. Heiser, "A survey of microarchitectural timing attacks and countermeasures on contemporary hardware," *Journal of Cryptographic Engineering*, vol. 8, pp. 1–27, 04 2018.

- [7] M. Ghaniyoun, K. Barber, Y. Xiao, Y. Zhang, and R. Teodorescu, "Teesec: Pre-silicon vulnerability discovery for trusted execution environments," in *ISCA*, ISCA '23, (New York, NY, USA), Association for Computing Machinery, 2023.

- [8] W. Wang, "Side channel risks in hardware trusted execution environments (tees)," in Side Channel Risks in Hardware Trusted Execution Environments (TEEs), May 2019. Presented at a research event.

- R.-V. International, The RISC-V Instruction Set Manual: Volume II: Privileged Architecture, Version 20240411, Apr. 2024, Section 3.7., April 2024.

- [10] D. A. Osvik, A. Shamir, and E. Tromer, "Cache attacks and countermeasures: the case of aes," in *CT-RSA*, CT-RSA'06, (Berlin, Heidelberg), p. 1–20, Springer-Verlag, 2006.

- [11] W.-M. Hu, "Reducing timing channels with fuzzy time," in *RISP*, pp. 8– 20, 1991.

- [12] E. Brickell, "Technologies to improve platform security," in CHES -Invited Talk, (Nara, Japan), Intel Corporation, September 2011.

- [13] W. Wu, E. Zhai, D. Jackowitz, D. Wolinsky, L. Gu, and B. Ford, "Warding off timing attacks in deterland," *ArXiv*, vol. abs/1504.07070, 2015.

- [14] A. Aviram, S.-C. Weng, S. Hu, and B. Ford, "Efficient system-enforced deterministic parallelism," *Commun. ACM*, vol. 55, p. 111–119, May 2012.

- [15] Y. Zhang and M. K. Reiter, "Düppel: retrofitting commodity operating systems to mitigate cache side channels in the cloud," in CCS, CCS '13, (New York, NY, USA), p. 827–838, Association for Computing Machinery, 2013.

- [16] D. E. Denning, "A lattice model of secure information flow," Commun. ACM, vol. 19, p. 236–243, May 1976.

- [17] M. Tiwari, X. Li, H. M. G. Wassel, F. T. Chong, and T. Sherwood, "Execution leases: A hardware-supported mechanism for enforcing strong non-interference," in 2009 42nd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), pp. 493–504, 2009.

- [18] Z. Wang and R. B. Lee, "New cache designs for thwarting software cache-based side channel attacks," *SIGARCH Comput. Archit. News*, vol. 35, p. 494–505, June 2007.

- [19] T. Kim, M. Peinado, and G. Mainar-Ruiz, "STEALTHMEM: System-Level protection against Cache-Based side channel attacks in the cloud," in USENIX Security, (Bellevue, WA), pp. 189–204, USENIX Association, Aug. 2012.

- [20] Z. Zhou, M. K. Reiter, and Y. Zhang, "A software approach to defeating side channels in last-level caches," in CCS, CCS '16, (New York, NY, USA), p. 871–882, Association for Computing Machinery, 2016.

- [21] S. Nashimoto, R. Ueno, and N. Homma, "Comparative analysis and implementation of jump address masking for preventing tee bypassing fault attacks," in *ARES*, ARES '24, (New York, NY, USA), Association for Computing Machinery, 2024.

# Verilog-A Compact Model of Ferroeletric Memory Devices For Compute-In-Place Applications

Poovendran Muthusamy, Chhandak Mukherjee, Marina Deng, Cristell Maneux, François Marc IMS Laboratory, University of Bordeaux, France.

*Abstract*—In the rapidly evolving field of nanoelectronics, ferroelectric memory devices have emerged as promising candidates for advancing compute-in-place (CIP) applications. By leveraging their unique characteristics, such as nonlinearity and hysteresis, these devices offer the potential to enhance memory architectures and improve computational efficiency. This research introduces a compact, current-based model for the ferroelectric capacitor (FeCAP), specifically developed to capture its complex behaviour and enable optimized performance in CIP applications. Implemented in Verilog-A, the model provides researchers and engineers with a powerful tool for simulating and designing energy-efficient memory architectures.

*Index Terms*—Ferroelectric Memory, Verilog-A Modelling, Compute-In-Place.

# I. INTRODUCTION

The rising demands in modern nanoelectronics call for memory architectures that can overcome Von Neumann bottleneck and energy inefficiencies. Compute-In-Place architectures, which integrate processing modules directly with the memory [1], offer a promising approach by reducing data transfer delay and computational load for the Micro Controller Unit (MCU), enhancing speed and energy efficiency. Ferroelectric memory devices have attracted considerable attention for these applications because of their unique properties: non-linearity, hysteresis, and non-volatility, which enable rapid switching and improved retention [2]. However, modelling these complex behaviours remains challenging. To address this, we introduce a compact, currentbased model for ferroelectric memory devices, implemented in Verilog-A. This current based model can accurately capture dynamic ferroelectric behaviour and has been previously validated through extensive simulations reproducing the behaviour of experimental data [3], paving the way for its integration into energy-efficient, high-performance computing systems. This work shows a new implementation of this model in Keysight ICCAP environment suitable for device compact modelling using Verilog-A description language.

# II. FERROELECTRIC MEMORY DEVICE

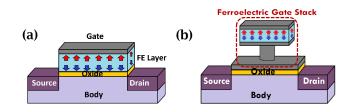

# A. Ferroelectric Memory Field Effect Transistor

As illustrated in Fig. 1, the ferroelectric capacitor is integrated directly on top of the CMOS gate to form Ferroelectric Memory Field Effect Transistor (FeMFET). This structure

Fig. 1. (a) Ferroelectric Field Effect Transistors (FeFET) where FE layer is stacked in CMOS gate, (b) Ferroelectric Memory Field Effect Transistor (FeMFET), formed by the integration of FeCAP on top of CMOS gate.

eliminates the interface layer that lies between the gate oxide and the ferroelectric material in the Ferroelectric Field Effect Transistors (FeFET)s — a layer often linked to increased imprint effects that can degrade device performance over time [4]. Eliminating this layer can significantly enhance endurance of the device. This improved endurance supports computein-place architectures by ensuring reliable operation during frequent switching cycles.

# III. COMPACT MODELLING

# A. Current based Preisach model

The current-based model captures the complex dynamics of the FeCAP by considering three main components of the current: ferroelectric current ( $I_{FE}$ ), leakage current ( $I_{leakage}$ ) and dielectric current ( $I_{DE}$ ) [5]. Among these, the ferroelectric current is modelled using the Lorentzian function, which provides an accurate representation of its behaviour under varying electrical conditions. Furthermore, the Polarization-Electric field (P-E) hysteresis loop is derived from the integration of the current, enabling detailed insights into the non-linear and hysteric properties of the FeCAP.

# B. Expressions and parameters used

In the following, the key equations and parameters used in the model are presented. The total current  $(I_{Total})$  is modelled as the sum of the three components as listed above is expressed in equation (1).

$$I_{\text{Total}} = I_{\text{FE}} + I_{\text{DE}} + I_{\text{leakage}} \tag{1}$$

Since leakage is negligible in ferroelectric devices,  $I_{leakage}$  is approximated to zero. In equation (2), surface area of

the capacitor is represented by S whereas  $t_{fe}$  denotes the ferroelectric layer thickness, while  $C_{DE}$  is the base capacitance and  $V_{off}$  is the offset voltage of FeCAP.

$$I_{DE} = C_{DE} \cdot \frac{dV}{dt} \quad \text{with} \quad C_{DE} = \frac{\epsilon_0 \cdot \epsilon_R \cdot S}{t_{fe}} \qquad (2)$$

The rate of change of polarization with respect to the electric field is given by dP/dE. The ferroelectric current is modelled using a Lorentzian function characterized by its amplitude (A) and width (w), with  $\pi$  used as a normalization factor as shown in equations (3) & (4).

$$\frac{dP^{\pm}}{dE} = \frac{2 \cdot A^{\pm} \cdot w^{\pm}}{4\pi (\left(E - E_c^{\pm}\right)^2 + \left(w^{\pm}\right)^2)} \tag{3}$$

$$I_{FE} = S \cdot \frac{dP}{dE} \cdot \frac{dE}{dt} \quad \text{with} \quad E = \frac{V_{applied} - V_{off}}{t_{fe}} \qquad (4)$$

These expressions and parameters together provide a robust framework for simulating the dynamic behaviour of ferroelectric memory devices. The permittivity of free space is given by  $\epsilon_0$  and  $\epsilon_R$  is the relative permittivity of the ferroelectric material used. The values of other parameters used in the model, obtained from experimental analysis [3], are presented in Table I.

TABLE I FITTING PARAMETERS VALUES AND FECAP DIMENSIONS

| A (C/m <sup>2</sup> ) | w (V/10nm)           | S (µm <sup>2</sup> )  | V <sub>off</sub> (V) |

|-----------------------|----------------------|-----------------------|----------------------|

| 0.36                  | 0.54                 | 306                   | 0.32                 |

| A <sub>Leak</sub>     | t <sub>fe</sub> (nm) | E <sub>c</sub> (V/nm) | $\epsilon_{ m R}$    |

| 0                     | 10                   | 0.179                 | 29.7                 |

# IV. VERILOG-A CODE AND RESULTS

# A. Verilog-A code used on ICCAP

The following Verilog-A code implements the ferroelectric capacitor model within the ICCAP simulation environment.

```

// Rate of change of Polarization (dP/dE)//

if (dV_dt > 0) begin

dP_dE = (2 * A_plus / `PI ) * (w_plus)

/ (4 * (V(p, n) - V_off - E_c_plus)**2 + w_plus**2);

end else if (dV_dt < 0 ) begin

dP_dE = (2 * A_minus / `PI ) * (w_minus)

/ (4 * (V(p, n) - V_off - E_c_minus)**2 + w_minus**2);

end

// Ferro current equation (I_fe)//

Ife = area * dE_dt * dP_dE ;

I(p,n) <+ Ife ;

// Polarization//

V(Pol) <+ idt(I(p,n)) / area;</pre>

```

# B. Simulated Results

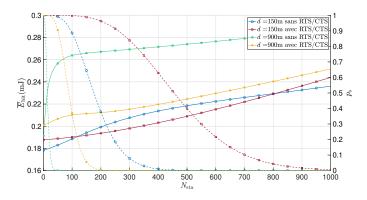

The simulation results of the FeCAP model in the Keysight ICCAP environment are presented below. Fig. 2 shows transient analysis under a ramp voltage, highlighting dynamic response of the ferroelectric capacitor. Fig. 3 presents the I-V characteristics, illustrating the relationship between applied voltage and current.

Fig. 2. Transient simulation of FeCAP using Verilog-A model in ICCAP

Fig. 3. I-V Characteristics of FeCAP Fig. 4. P-V Characteristics of FeCAP

Additionally, polarization is simulated by integrating the current within the model, and the results obtained are shown in Fig. 4.

# CONCLUSION

This work presents a compact Verilog-A model for Fe-CAPs, readily usable with SPICE tools, and capable of accurately simulating ferroelectric polarization. The model supports compute-in-place architectures by ensuring reliable and efficient operation during frequent switching cycles. The validation is anticipated in the near future with experimental data.

## ACKNOWLEDGMENT

This work has received state aid managed by the Agence Nationale de la Recherche (ANR) under France 2030, referring to ANR-23-PEEL-0003.

- J. P. Noel et al., "Compute-In-Place Serial FeRAM: Enhancing Performance, Efficiency, and Adaptability in Critical Embedded Systems," IEEE VLSI-SoC, 2023.

- [2] Chenming Hu et al., "Ferroelectric HfO<sub>2</sub> Memory Transistors With High-k Interfacial Layer and Write Endurance Exceeding 10<sup>10</sup> Cycles," IEEE Electron Device Letters, 2021.

- [3] M. Bocquet et al., "Memory Window in Si:HfO<sub>2</sub> FeRAM Arrays: Performance Improvement and Extrapolation at Advanced Nodes," in Proc. IEEE Int. Memory Workshop (IMW), 2023.

- [4] Y. Zhou et al., "Mechanisms of imprint effect on ferroelectric thin films" J. Appl. Phys., 2005.

- [5] I. Fina et al., "Non-ferroelectric Contributions to the Hysteresis Cycles in Manganite Thin Films: A Comparative Study of Measurement Techniques," J. Appl. Phys., 2011.

# Modélisation de la consommation énergétique d'une station dans un réseau Wi-Fi HaLow

Sébastien Maudet, Guillaume Andrieux, Jean-François Diouris Université de Nantes, CNRS, IETR UMR 6164, F-85000 La Roche-sur-Yon, France sebastien.maudet@univ-nantes.fr

Abstract—Le déploiement d'un réseau IoT est soumis à des contraintes de consommation énergétique. Pour minimiser les coûts de service, il est essentiel d'optimiser la durée de vie des objets, qui sont souvent alimentés par des sources d'énergie peu fiables. Cette optimisation doit s'appuyer sur des modèles finement ajustés qui prennent en compte toutes les spécificités de la transmission d'un objet connecté. Dans cette étude, un modèle de consommation d'énergie est proposé pour le protocole 802.11ah. Ce dernier est basé sur des mesures réalisées in-situ et les résultats montrent l'influence du nombre de stations sur la consommation d'énergie d'une station.

# Index Terms-Énergie; IoT; Wi-Fi HaLow; IEEE 802.11ah.

# I. INTRODUCTION

L'efficacité énergétique est l'un des principaux défis de l'IoT. Dans ce type de réseau, le nombre d'appareils est important, ils sont géographiquement dispersés et l'accès à l'énergie n'est pas fiable. La norme Wi-Fi HaLow a été spécifiquement conçue pour répondre à ces besoins et elle hérite des principales caractéristiques du protocole Wi-Fi.

Au niveau de la couche physique, les transmissions sont réalisées dans des bandes de fréquence inférieures à 1 GHz, avec une modulation OFDM (*Orthogonal Frequency Division Modulation*) dont les caractéristiques sont dans un rapport de 10 avec la norme 802.11ac. La portée est estimée à 1 km et le débit entre 150 kbit/s et 78 Mbit/s. Une bande passante à 1 MHz a été ajoutée afin d'augmenter la portée de transmission et améliorer la consommation d'énergie [1], [2].